Advanced Capabilities

The Barrage™ Relay Advantage

Barrage™ Relay is one of TrellisWare’s core technologies. It is U.S. patented, and has become a trusted, proven TRL-9 technology that is currently deployed in networks for military and commercial operations all over the world. Barrage Relay works as a spectrally efficient Mobile Ad Hoc Network (MANET). It is effective for dynamic networks because it does not rely on infrastructure, pre-planning, or routing to provide tactical users with voice, data sharing, and situational awareness while allowing for network scalability and adaptability.

Barrage Relay AdvantageSpecial Communications

TrellisWare’s special communications team supports customers with restricted or classified requirements or missions, often customizing TrellisWare products, technologies, or capabilities for those markets. TrellisWare supports these special needs customers in designing custom solutions that may benefit from our advancements in commercial technology, drawing from our waveform expertise to our small packaging capability.

Interference Cancellation

Many critical military and commercial situations need interference cancellation for receiving a weak signal in the presence of a strong interferer. TrellisWare delivers solutions ranging from passive non-linear cancellation to active-adaptive interference cancellation.

F-LDPC FEC Licensing

TrellisWare’s capacity-approaching Forward Error Correcting (FEC) cores are available for licensing to meet today’s communication systems requirements. These high performance, low complexity Flexible-Low Density Parity Check (F-LDPC) error correction IP cores are currently incorporated into commercial and Department of Defense (DoD) waveforms.

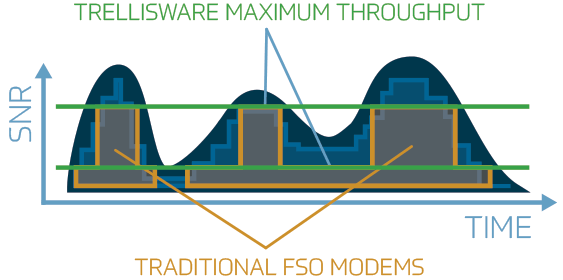

More InfoFREE SPACE OPTICS (FSO)

TrellisWare’s Free Space Optics (FSO) processor is a Layer 1 and Layer 2 solution for combating scintillation induced slow fading of the free space optics channel. It combines TrellisWare’s F-LDPC code and a hybrid ARQ protocol to track channel scintillation and adjust code rate and throughput. The FSO modems are designed for easy integration, are applicable for high-speed RF and optical systems.

Free Space Optics

WANT TO IMPROVE YOUR COMMUNICATIONS?

Contact TrellisWare to find out how our broad range of capabilities can meet your mission challenges.